PCB的电路设计与绘制技巧

时间:2015-12-04 22:11 来源:未知 作者:admin 点击:次

1、如果设计的电路系统中包含FPGA器件,则在绘制原理图前必需使用Quartus II软件对管脚分配进行验证。(FPGA中某些特殊的管脚是不能用作普通IO的)。 5V一般可能是电源输入,只需要在一小块区域内铺铜。且尽量粗(你问我该多粗——能多粗就多粗,越粗越好);

1.2V和1.8V是内核电源(如果直接采用线连的方式会在面临BGA器件时遇到很大困难),布局时尽量将1.2V与1.8V分开,并让1.2V或1.8V内相连的元件布局在紧凑的区域,使用铜皮的方式连接,如图: 5、模拟数字要隔离,怎么个隔离法?布局时将用于模拟信号的器件与数字信号的器件分开,然后从AD芯片中间一刀切! 模拟信号铺模拟地,模拟地/模拟电源与数字电源通过电感/磁珠单点连接。

6、基于PCB设计软件的PCB设计也可看做是一种软件开发过程,软件工程最注重“迭****发”的思想,我觉得PCB设计中也可以引入该思想,减少PCB错误的概率。 (1) 原理图检查,尤其注意器件的电源和地(电源和地是系统的血脉,不能有丝毫疏忽); (2) PCB封装绘制(确认原理图中的管脚是否有误); (3) PCB封装尺寸逐一确认后,添加验证标签,添加到本次设计封装库; (4) 导入网表,边布局边调整原理图中信号顺序(布局后不能再使用OrCAD的元件自动编号功能); (5) 手工布线(边布边检查电源地网络,前面说过:电源网络使用铺铜方式,所以少用走线); 总之,PCB设计中的指导思想就是边绘制封装布局布线边反馈修正原理图(从信号连接的正确性、信号走线的方便性考虑)。 7、晶振离芯片尽量近,且晶振下尽量不走线,铺地网络铜皮。多处使用的时钟使用树形时钟树方式布线。

8、连接器上信号的排布对布线的难易程度影响较大,因此要边布线边调整原理图上的信号(但千万不能重新对元器件编号)。 (1) 使用排线连接:上下接口一致;

(2) 直插座:上下接口镜像对称,如下图: 10、模块连接信号的设计: (1) 若2个模块放置在PCB同一面,则管教序号大接小小接大(镜像连接信号); (2) 若2个模块放在PCB不同面,则管教序号小接小大接大。

这样做能放置信号像上面的右图一样交叉。当然,上面的方法不是定则,我总是说,凡事随需而变(这个只能自己领悟),只不过在很多情况下按这种方式设计很管用罢了。

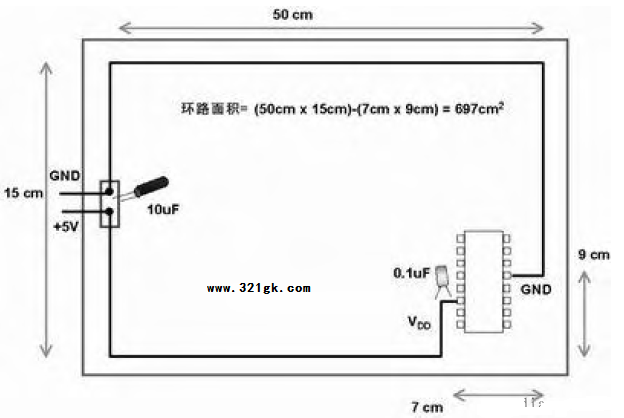

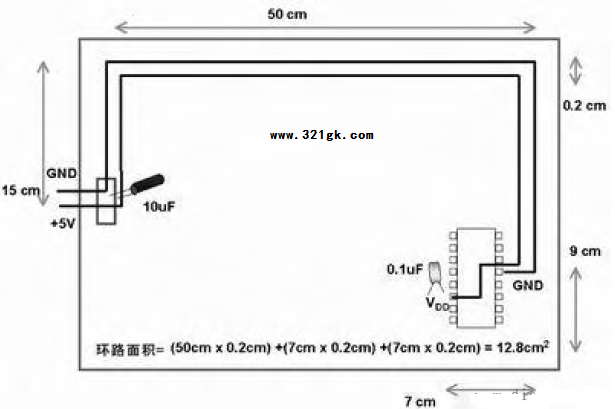

上图的电源地回路面积大,容易受电磁干扰。 上图通过改进——电源与地线靠近走线,减小了回路面积,降低了电磁干扰(679/12.8,约54倍)。因此,电源与地尽量应该靠近走线!而信号线之间则应该尽量避免并行走线,降低信号之间的互感效应。 (责任编辑:admin) |