模拟集成电路设计流程-二极管由管芯管壳和两个电极构成

时间:2017-02-27 10:06 来源:未知 作者:admin 点击:次

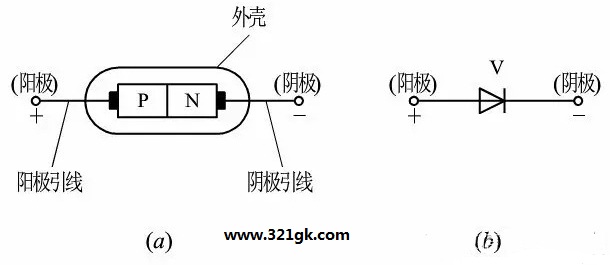

| 模拟集成电路设计主要是通过有经验的设计师进行手动的电路调试模拟而得到,与此相对应的数字集成电路设计大部分是通过使用硬件描述语言在eda软件的控制下自动的综合产生。 数字集成电路和模拟集成电路的区别在于数字集成电路主要是针对数字信号处理的模块。如计算机里的2进制、8进制、10进制、16进制的数据进行处理的集成模块。数字集成电路的运行以开关状态经行运算,它的精度高适合复杂的计算。模拟集成电路主要是针对模拟信号处理的模块。如话筒里的声音信号,电视信号和vcd输出的图象信号、温度采集的模拟信号和其它模拟量的信号处理的集成模块。 模拟集成电路主要是指由电容、电阻、晶体管等组成的模拟电路集成在一起用来处理模拟信号的集成电路。有许多的模拟集成电路,如运算放大器、模拟乘法器、锁相环、电源管理芯片等。模拟集成电路的主要构成电路有:放大器、滤波器、反馈电路、基准源电路、开关电容电路等。模拟集成电路工作在晶体管的三角放大区。 集成电路设计的流程一般先要进行软硬件划分,将设计基本分为两部分:芯片硬件设计和软件协同设计。芯片硬件设计包括: 1.功能设计阶段。 设计人员产品的应用场合,设定一些诸如功能、操作速度、接口规格、环境温度及消耗功率等规格,以做为将来电路设计时的依据。更可进一步规划软件模块及硬件模块该如何划分,哪些功能该整合于SOC 内,哪些功能可以设 计在电路板上。 2.设计描述和行为级验证 供能设计完成后,可以依据功能将SOC 划分为若干功能模块,并决定实现这些功能将要使用的IP 核。此阶段将接影响了SOC 内部的架构及各模块间互动的讯号,及未来产品的可靠性。 决定模块之后,可以用VHDL 或Verilog 等硬件描述语言实现各模块的设计。接着,利用VHDL 或Verilog 的电路仿真器,对设计进行功能验证(function simulation,或行为验证 behavioral simulation)。 注意,这种功能仿真没有考虑电路实际的延迟,但无法获得精确的结果。 3.逻辑综合 确定设计描述正确后,可以使用逻辑综合工具(synthesizer)进行综合。 综合过程中,需要选择适当的逻辑器件库(logic cell library),作为合成逻辑电路时的参考依据。 硬件语言设计描述文件的编写风格是决定综合工具执行效率的一个重要因素。事实上,综合工具支持的HDL 语法均是有限的,一些过于抽象的语法只适于作为系统评估时的仿真模型,而不能被综合工具接受。 逻辑综合得到门级网表。 4.门级验证(Gate-Level Netlist Verification) 门级功能验证是寄存器传输级验证。主要的工作是要确认经综合后的电路是否符合功能需求,该工作一般利用门电路级验证工具完成。 注意,此阶段仿真需要考虑门电路的延迟。 5.布局和布线 布局指将设计好的功能模块合理地安排在芯片上,规划好它们的位置。布线则指完成各模块之间互连的连线。 注意,各模块之间的连线通常比较长,因此,产生的延迟会严重影响SOC的性能,尤其在0.25 微米制程以上,这种现象更为显著。 目前,这一个行业仍然是中国的空缺,开设集成电路设计与集成系统专业的大学还比较少,其中师资较好的学校有 上海交通大学,哈尔滨工业大学,黑龙江大学、东南大学,西安电子科技大学,电子科技大学,哈尔滨理工大学,复旦大学,华东师范大学等。 这个领域已经逐渐饱和,越来越有趋势走上当年软件行业的道路。 模拟集成电路设计的一般过程: 1.电路设计 依据电路功能完成电路的设计。 2.前仿真 电路功能的仿真,包括功耗,电流,电压,温度,压摆幅,输入输出特性等参数的仿真。 3.版图设计(Layout) 依据所设计的电路画版图。一般使用Cadence软件。 4.后仿真 对所画的版图进行仿真,并与前仿真比较,若达不到要求需修改或重新设计版图。 5.后续处理 将版图文件生成GDSII文件交予Foundry流片。 二极管由管芯管壳和两个电极构成 二极管由管芯、管壳和两个电极构成。管芯就是一个PN结,在PN结的两端各引出一个引线,并用塑料、玻璃或金属材料作为封装外壳,就构成了晶体二极管,如下图所示。P区的引出的电极称为正极或阳极,N区的引出的电极称为负极或阴极。  (责任编辑:admin) |