谁消耗了所有的dB? 计算机8位A/D转换器ADC0809

时间:2017-03-15 08:28 来源:未知 作者:admin 点击:次

很多时候,ADC(模数转换器)在–1 dBFS时具有额定性能。一些数据手册给出的失真比满量程低0.5 dB。无论是比满量程低1 dB或0.5 dB,如果在满量程(0 dBFS)下运行ADC输入,这样做可防止信号发生削波。台式RF信号发生器通常以dBm为单位输出信号。为了在1.7 V p-p满量程ADC范围内实现–1 dBFS,信号电平仅需7.6 dBm(基于50 Ω基准阻抗)。不过,这样做时,ADC的单音FFT输出显示为–6.7 dBFS。是什么消耗了所有的dB?

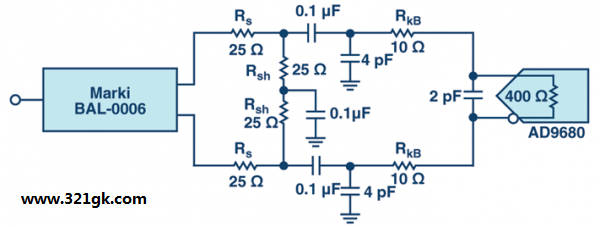

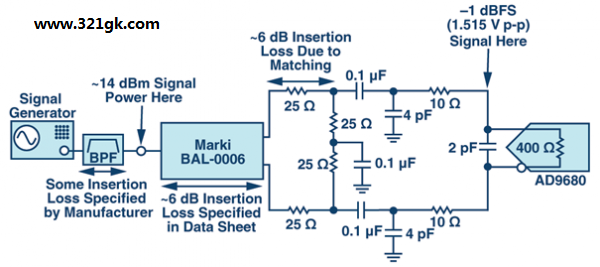

答案显而易见,即ADC部件。就是ADC的前端网络。让我们进一步看看用于ADCAD9680的默认前端网络。 将单端转换为差分模式可通过宽带巴伦BAL-0006SMG实现。简单看下BAL-0006SMG数据手册,显示它具有6 dB插入损耗。继巴伦之后的匹配网络(Rs和RSH)添加了另一个6 dB。该匹配网络需要提供宽带匹配至巴伦输出。ADC (RkB)前方的串联电阻呈现少量插入损耗。该电阻通过降低ADC采样级到保持级的反冲来提高第三次谐波性能。

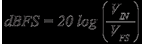

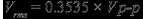

因此,让我们克服相关ADC难题以了解信号发生器获得–1 dBFS ADC信号时所需功率。50 Ω基准电阻用于以下数学方程。对于1.7 Vp-p的默认满量程电平,–1 dBFS信号为1.515 Vp-p。由于10 Ω电阻损耗相当小,我们可以假设该损耗电压为端接网络电压。巴伦端接具有6 dB损耗,因此巴伦的每一侧摆幅约为1.515 V的两倍。这导致单端输入约为3.03 Vp-p。因此,信号发生器须提供对应于约3.03 Vp-p或14 dBm的信号。请注意,这不包括带通滤波器或连接器电缆的插入损耗。因此,再次看下图1,这次我们通过一些注释得到图2。 再次回到我们的问题上,如果ADC前方的信号发生器旁边没有任何干扰,则获得-1 dBFS ADC信号所需功率为7.6 dBm的前提是正确的。可能需考虑巴伦。现在有其它因素(宽带巴伦、匹配网络、反冲控制等)会影响插入损耗,从而导致在-6.7 dBFS时产生衰减信号。因此,您可以放心的说"我的前端消耗了所有的dB"。如您所见,数学方程从不会错。

参考以下等公式:

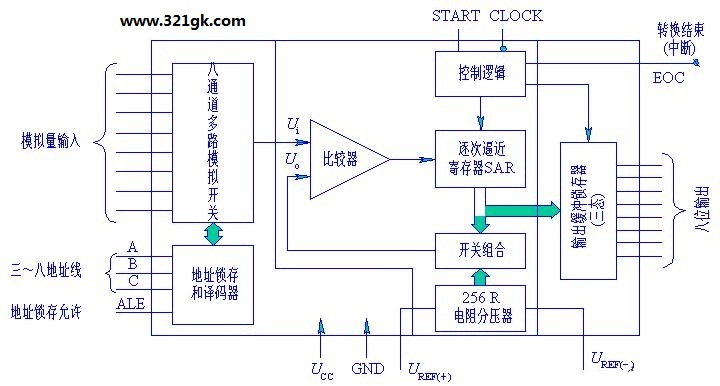

图1 ADC0808/0809的原理框图

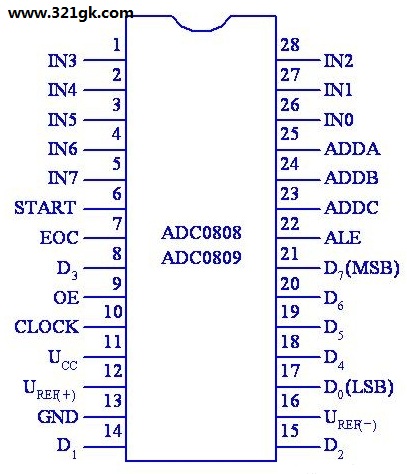

2. ADC0808/0809的外引脚功能

ADC0808/0809的管脚排列如图2所示,其主要管脚的功能如下:

IN0~IN7——8个模拟量输入端。

START——启动A/D转换器,当START为高电平时,开始A/D转换。

EOC——转换结束信号。当A/D转换完毕之后,发出一个正脉冲,表示A/D转换结束。

此信号可作为A/D转换是否结束的检测信号或中断申请信号。

OE——输出允许信号。如果此信号被选中,则允许从A/D转换器的锁存器中读取数字量。

CLOCK——时钟信号。

ALE——地址锁存允许,高电平有效。当ALE为高电平时,允许C、B、A所示的通道被选中,并将该通道的模拟量接入A/D转换器。

ADDA、ADDB、ADDC——通道号地址选择端,C为最高位,A为最低位。当C、B、A为全零(000)时,选中IN0通道接入;为001时,选中IN1通道接入;为111时,选中IN7通道接入。

D7~D0——数字量输出端。

UREF(+)、UREF(-)——参考电压输入端,分别接+、-极性的参考电压,用来提供D/A转换器权电阻的标准电平。在模拟量为单极性输入时, UREF(+)=5V,UREF(-)=0V;当模拟量为双极性输入时,UREF(+) =+5V,UREF(-) =-5V。

|