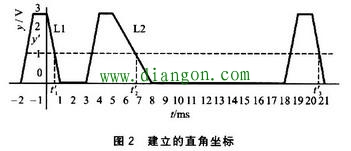

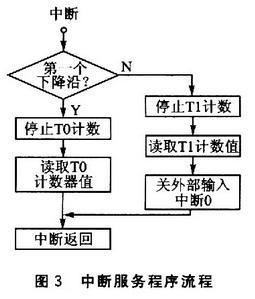

51单片机的外部中断有两种触发方式可选:电平触发和边沿触发。选择电平触发时,单片机在每个机器周期检查中断源口线,检测到低电平,即置位中断请求标志,向CPU请求中断。选择边沿触发方式时,单片机在上一个机器周期检测到中断源口线为高电平,下一个机器周期检测到低电平,即置位中断标志,请求中断。 这个原理很好理解。但应用时需要特别注意的几点: 1)电平触发方式时,中断标志寄存器不锁存中断请求信号。 也就是说,单片机把每个机器周期的S5P2采样到的外部中断源口线的电平逻辑直接赋值到中断标志寄存器。标志寄存器对于请求信号来说是透明的。这样当中断 请求被阻塞而没有得到及时响应时,将被丢失。换句话说,要使电平触发的中断被CPU响应并执行,必须保证外部中断源口线的低电平维持到中断被执行为止。因 此当CPU正在执行同级中断或更高级中断期间,产生的外部中断源(产生低电平)如果在该中断执行完毕之前撤销(变为高电平)了,那么将得不到响应,就如同 没发生一样。同样,当CPU在执行不可被中断的指令(如RETI)时,产生的电平触发中断如果时间太短,也得不到执行。 2)边沿触发方式时,中断标志寄存器锁存了中断请求。中断口线上一个从高到低的跳变将记录在标志寄存器中,直到CPU响应并转向该中断服务程序时,由硬件自动清除。因此当CPU正在执行同级中断(甚至是外部中断本身)或高级中断时,产生的外部中断(负跳变)同样将被记录在中断标志寄存器中。在该中断退出后,将被响应执行。如果你不希望这样,必须在中断退出之前,手工清除外部中断标志。 3)中断标志可以手工清除。一个中断如果在没有得到响应之前就已经被手工清除,则该中断将被CPU忽略。就如同没有发生一样。 4)选择电平触发还是边沿触发方式应从系统使用外部中断的目的上去考虑,而不是如许多资料上说的根据中断源信号的特性来取舍。比如,有的书上说(《KeilC51使用技巧及实战》),就有类似的观点。 MCS51单片机系列属于8位单片机,它是Intel公司继MCS48系列的成功设计之后,于1980年推出的产品。由于MCS51系列具有很强的片内功能和指令系统,因而使单片机的应用发生了一个飞跃,这个系列的产品也很快成为世界上第二代的标准控制器。51系列单片机有5个中断源,其中有2个是外部输入中断源INT0和INT1。可由中断控制寄存器TCON的IT1(TCON.2)和IT0(TCON.1)分别控制外部输入中断1和中断0的中断触发方式。若为0,则外部输入中断控制为电平触发方式;若为1,则控制为边沿触发方式。这里是下降沿触发中断。 1、问题的引出 几 乎国内所有的单片机资料对单片机边沿触发中断的响应时刻方面的定义都是不明确的或者是错误的。例如文献[1]中关于边沿触发中断响应时刻的描述为“对于脉 冲触发方式(即边沿触发方式)要检测两次电平,若前一次为高电平,后一次为低电平,则表示检测到了负跳变的有效中断请求信号”,但实际情况却并非如此。 我们知道,单片机外部输入的中断触发电平是TTL电平。对于TTL电平,TTL逻辑门输出高电平的允许范围为2.4~5V,其标称值 为3.6V;输出低电平的允许范围为0~0.7V,其标称值为0.3V[2],在0.7V与2.4V之间的是非高非低的中间电平。 这 样,在实际应用中,假设单片机外部中断引脚INT0输入一路由+5V下降到0V的下降沿信号,单片机在某个时钟周期采样INT0引脚得到2.4V的 高电平;而在下一个时钟周期到来进行采样时,由于实际的外部输入中断触发信号由高电平变为低电平往往需要一定的时间,因此,检测到的可能并非真正的低电平 (小于0.7V),而是处于低电平与高电平之间的某一中间电平,即0.7~2.4V的某一电平。对于这种情况,单片机是否会依然置位中断触发标志从而 引发中断呢?关于这一点,国内的绝大部分教材以及单片机生产商提供的器件资料都没有给予准确的定义,但在实际应用中这种情况确实会碰到。 以美国Analog公司生产的运算放大器芯片AD708为例,其转换速率(slewrate)为0.3V/μs,在由AD708芯片组成的比较器电路中, 其输出方波的下降沿由2.4V下降到0.7V,所需时间约为:(2.4V-0.7V)/0.3V·μs-1=4.67μs。即需要 约4.67μs的过渡时间,下降沿才真正地由高电平下降为低电平,在实际应用电路中,这个下降时间往往可达10μs以上。对于精密的测量系统,这么 长的不确定时间是无法接受的,因此,有必要对单片机边沿中断触发时刻进行精确的测定。 2、测试波形的设计与分析 为了测定MCS51单片机下降沿触发的实际时刻,使用Agilent公司生产的型号为33250A的80MHz函数/任意波形发生器(function/arbitrarywaveformgenerator),产生出如图1所示的周期为20ms的周期波形。

|

51单片机边沿触发和电平触发的区别图解

时间:2018-04-04 10:47来源:未知 作者:admin 点击:

次

51单片机的外部中断有两种触发方式可选:电平触发和边沿触发。选择电平触发时,单片机在每个机器周期检查中断源口线,检测到低电平,即置位中断请求标志,向CPU请求中断。选择

顶一下

(0)

0%

踩一下

(0)

0%

------分隔线----------------------------

- 发表评论

-

- 最新评论 进入详细评论页>>