工业以太网PCB线路布局布线图解

时间:2015-12-10 09:11 来源:未知 作者:admin 点击:次

我们现今使用的网络接口均为以太网接口,目前大部分处理器都支持以太网口。目前以太网按照速率主要包括10M、10/100M、1000M三种接口,10M应用已经很少,基本为10/100M所代替。目前我司产品的以太网接口类型主要采用双绞线的RJ45接口,且基本应用于工控领域,因工控领域的特殊性,所以我们对以太网的器件选型以及PCB设计相当考究。从硬件的角度看,以太网接口电路主要由MAC(Media Access Controlleroler)控制和物理层接口(Physical Layer,PHY)两大部分构成。大部分处理器内部包含了以太网MAC控制,但并不提供物理层接口,故需外接一片物理芯片以提供以太网的接入通道。面对如此复杂的接口电路,相信各位硬件工程师们都想知道该硬件电路如何在PCB上实现。

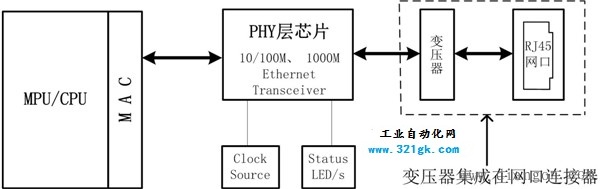

下图 1以太网的典型应用。我们的PCB设计基本是按照这个框图来布局布线,下面我们就以这个框图详解以太网有关的布局布线要点。

揭秘以太网接口在印制电路板上的实现

图 1 以太网典型应用

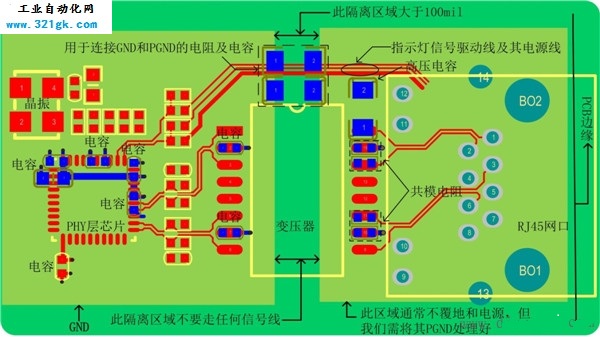

1. 图 2网口变压器没有集成在网口连接器里的参考电路PCB布局、布线图,下面就以图 2介绍以太网电路的布局、布线需注意的要点。

揭秘以太网接口在印制电路板上的实现

图 2变压器没有集成在网口连接器的电路PCB布局、布线参考

a) RJ45和变压器之间的距离尽可能的短,晶振远离接口、PCB边缘和其他的高频设备、走线或磁性元件周围,PHY层芯片和变压器之间的距离尽可能短,但有时为了顾全整体布局,这一点可能比较难满足,但他们之间的距离最大约10~12cm,器件布局的原则是通常按照信号流向放置,切不可绕来绕去;

b) PHY层芯片的电源滤波按照要芯片要求设计,通常每个电源端都需放置一个退耦电容,他们可以为信号提供一个低阻抗通路,减小电源和地平面间的谐振,为了让电容起到去耦和旁路的作用,故要保证退耦和旁路电容由电容、走线、过孔、焊盘组成的环路面积尽量小,保证引线电感尽量小;

c) 网口变压器PHY层芯片侧中心抽头对地的滤波电容要尽量靠近变压器管脚,保证引线最短,分布电感最小;

d) 网口变压器接口侧的共模电阻和高压电容靠近中心抽头放置,走线短而粗(≥15mil);

e) 变压器的两边需要割地:即RJ45连接座和变压器的次级线圈用单独的隔离地,隔离区域100mil以上,且在这个隔离区域下没有电源和地层存在。这样做分割处理,就是为了达到初、次级的隔离,控制源端的干扰通过参考平面耦合到次级;

f) 指示灯的电源线和驱动信号线相邻走线,尽量减小环路面积。指示灯和差分线要进行必要的隔离,两者要保证足够的距离,如有空间可用GND隔开;

g) 用于连接GND和PGND的电阻及电容需放置地分割区域。

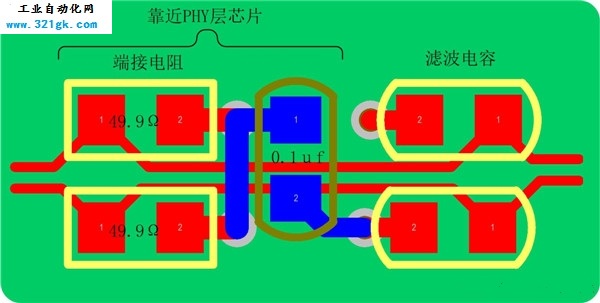

2. 以太网的信号线是以差分对(Rx±、Tx±)的形式存在,差分线具有很强共模抑制能力,抗干扰能力强,但是如果布线不当,将会带来严重的信号完整性问题。下面我们来一一介绍差分线的处理要点:

a) 优先绘制Rx±、Tx±差分对,尽量保持差分对平行、等长、短距,避免过孔、交叉。由于管脚分布、过孔、以及走线空间等因素存在使得差分线长易不匹配,时序会发生偏移,还会引入共模干扰,降低信号质量。所以,相应的要对差分对不匹配的情况作出补偿,使其线长匹配,长度差通常控制在5mil以内,补偿原则是哪里出现长度差补偿哪里;

b) 当速度要求高时需对Rx±、Tx±差分对进行阻抗控制,通常阻抗控制在100Ω±10%;

c) 差分信号终端电阻(49.9Ω,有的PHY层芯片可能没有)必须靠近PHY层芯片的Rx±、Tx±管脚放置,这样能更好的消除通信电缆中的信号反射;

d) 差分线对上的滤波电容必须对称放置,否则差模可能转成共模,带来共模噪声,且其走线时不能有stub ,这样才能对高频噪声有良好的抑制能力。

揭秘以太网接口在印制电路板上的实现

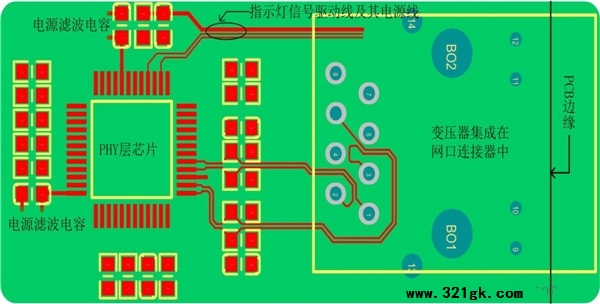

3. 变压器集成在连接器的以太网电路的PCB布局、布线较不集成的相对简单很多,下图 3是采用一体化连接器的网口电路的PCB布局、布线参考图:

揭秘以太网接口在印制电路板上的实现

图 3一体化连接器的网口PCB布局、布线参考图

从上图可以看出,图 3和图 1的不同之处在于少了网口变压器,其它大体相同。不同之处主要体现在网口变压器已集成至连接器里,所以地平面无需进行分割处理,但我们依然需要将一体化连机器的外壳连接到连续的地平面上。

以太网布局布线方面的要大致就这些,好的PCB布局布线不仅可以保证电路性能,还可以提高电路性能,笔者水平有限,不足之处欢迎指正交流。

(责任编辑:admin) |