NE555时基电路原理框图及引脚功能图解

时间:2018-06-21 08:53来源:未知 作者:admin 点击:

次

NE555时基电路,为电压比较器和R-S基本触发器的混成电路,可方便地构成单稳态(延时、定时)电路、双稳态(开关)电路及无稳态(振荡)电路。其构成电路之简便和应用之广,素有万

NE555时基电路,为电压比较器和R-S基本触发器的混成电路,可方便地构成单稳态(延时、定时)电路、双稳态(开关)电路及无稳态(振荡)电路。其构成电路之简便和应用之广,素有“万能电路”之称。

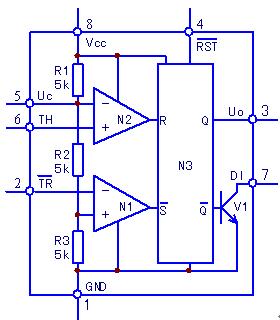

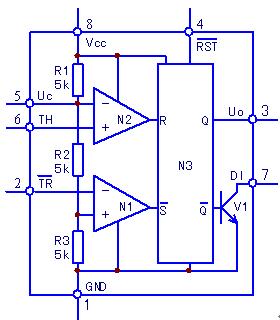

图 NE555时基电路原理框图及引脚功能

如上图所示,R1、R2、R3对供电Vcc分压,使N1比较器基准端(同相输入端)电压为1/3Vcc,N2基准端(反相输入端)电压为2/3Vcc。芯片5脚为调整端,接入上拉或下拉电阻时,可改变两个基准端电压的高低。两路比较器的输出端与R-S触发器的置位和复位相接,从而决定芯片3脚输出端的电平状态。当芯片2脚(/TR端)输入信号电压低于1/3Vcc时,N1输出端为“0”,R-S触发器被置位,芯片3脚变高电平,(在复位信号未输入之前)并保持;当芯片6脚输入电压高于2/3Vcc时,N2输出端为“1”,R-S触发器被复位(在置位信号未输入之前)并保持。芯片4为优先复位端(低电平有效),不用时可接Vcc。

显然,作为开关电路应用时,只要控制芯片2脚电压低于1/3Vcc,电路处于“开”态(3脚为“1”);控制芯片6脚高于2/3Vcc,电路即处于“关”态(3脚为“0”),即为开关(双稳态)电路。

(责任编辑:admin) |

织梦二维码生成器

------分隔线----------------------------